137***697

目前:

目前:

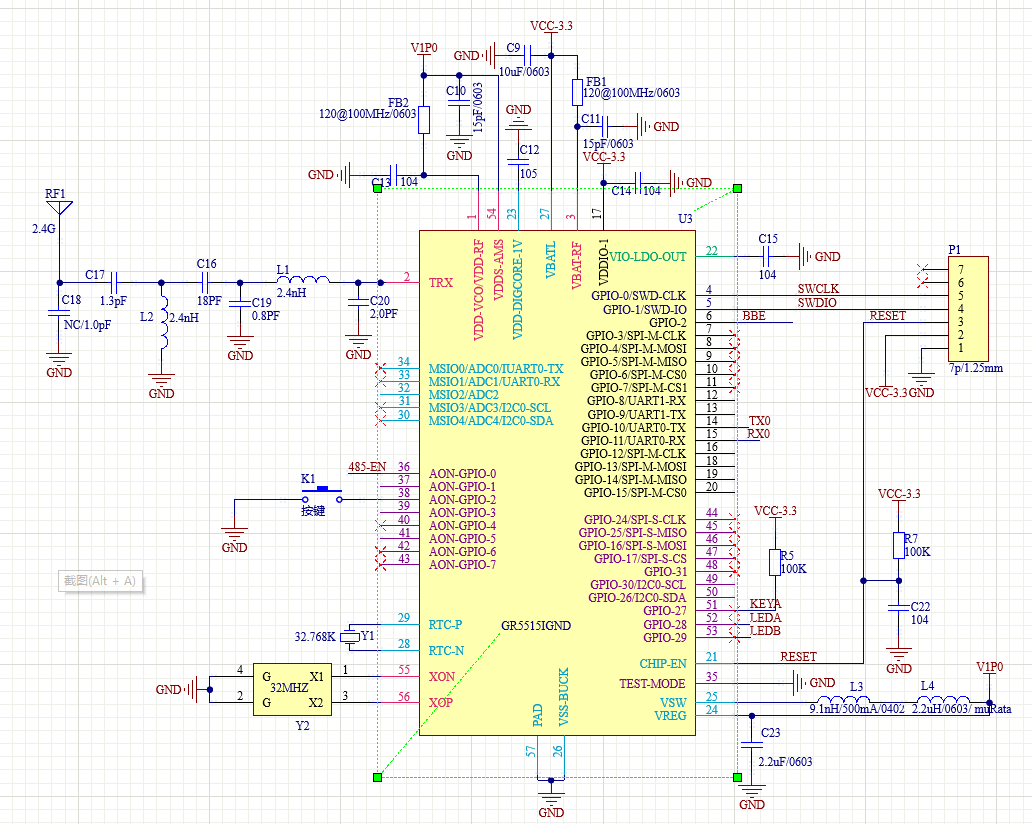

VBATL引脚 : 3.3v

DC-DC VREG引脚: 1.3v

VIO_LDO_OUT :3.3v

两个晶振均有工作

有时候上电一段时间会工作,但是工作一小段时间会死机

Van

hi

死机是一个系统性的问题,通过你的描述,可先从硬件设计入手

1:DC-DC VREG引脚: 1.3v---这个电压偏高,典型值约1.12v

VIO_LDO_OUT :3.3v -----LDO输出异常,典型值为1.85v,

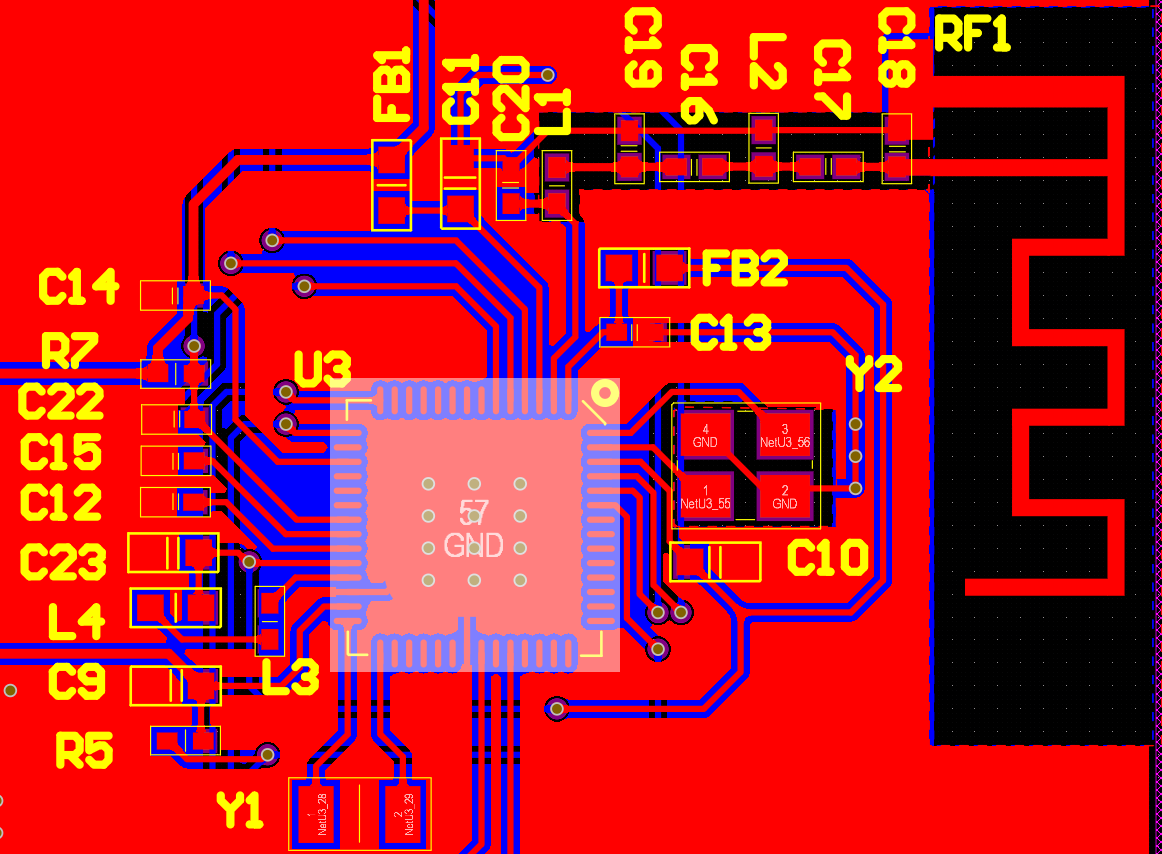

2:通过PCB截图,可以看到设计不合理,各电源回流路径比较差:

DC-DC /LDO 输出地与输入地非最优路径,

RF 电路参考地未放置地空

晶振未放置地孔,

更多硬件设计规范请参考《GR551x 硬件设计指南》。

另外请联系代理商或我司FAE 窗口进行原理图及PCB 评审(在线或邮件评审),将硬件风险排除掉再来观测死机问题,

打开微信,使用“扫一扫”即可关注