903***645

Hi Goodix

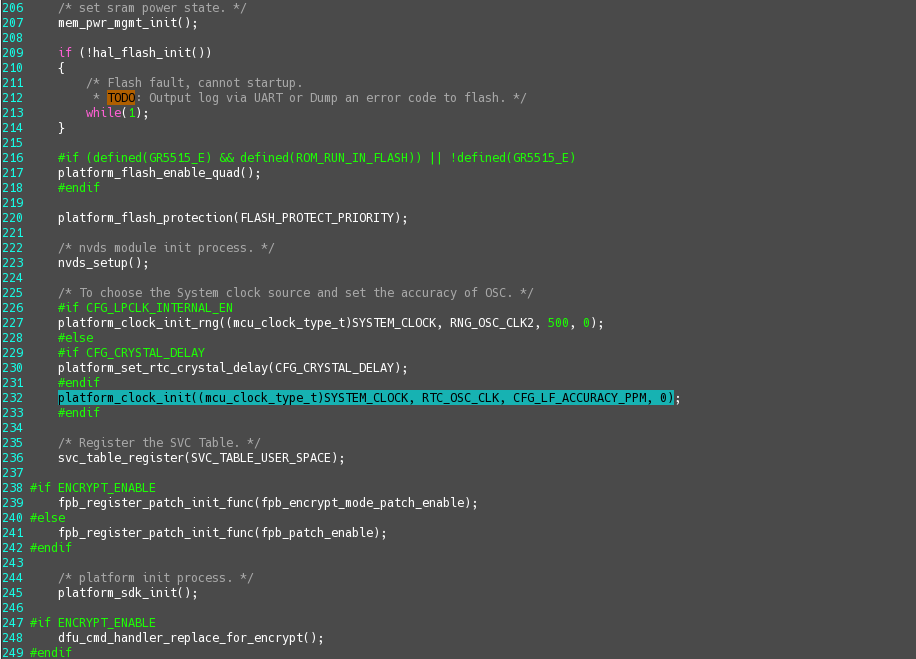

I use the Goodix GR5515I0ND chip with external flash memory XTX XT25F64B (Serial NOR Flash Memory 64Mbit 8192 Kbyte - recommendedet in "GR5515I0ND Series Flash Selection Guide") ). I built a simple project to blink the LED, but after flashing the LED did not blink. I used a version of the SDK 1.6.12 where this project is located in the GR551x_SDK_V1.6.12/projects/peripheral/gpio/gpio_led directory. Keil MDK was used to build the project. The flash chip was connected to pins 43-48 of the GR5515I0ND. After connecting the debugger it was found that the code does not even get to the function "main()" and suddenly breaks down inside the function "platform_init(void)" when calling the nested function (line 232 highlighted in the screenshot) with the arguments :

platform_clock_init((mcu_clock_type_t)SYSTEM_CLOCK, RTC_OSC_CLK, CFG_LF_ACCURACY_PPM, 0);

from file GR551x_SDK_V1.6.12/toolchain/gr551x/source/platform_gr55xx.c.

I also found out that this crash is related to aon_watchdog triggering and following full CPU reset, because platform_clock_init() either runs too long or can't complete its execution at all. I suspect that this has to do with wrong settings in the "custom_config.h" file and the fact that the external SPI flash memory used is not configured correctly. I tried changing many settings in "custom_config.h", but I didn't notice any effect at all.

Also in custom_config.h can define

#define GR5515_D

#define GR5515_C

#define GR5515_E

But which of these definitions refers to GR5515I0ND? I couldn't find a description in any available manuals. I don't understand which one is better and I used GR5515_D.

Please help me to understand.

Barton

Hi Osipov,

I‘m very sorry that we did not answer your questions in a timely manner.

1. If there is no external crystal,you can Enable internal osc as low power clock,by

“CFG_LPCLK_INTERNAL_EN”;

2. In GR551x_SDK_V1.6.12, GR5515_C and GR5515_E are invalid definations, please select GR5515_D, thanks.

Barton

Hi,

Thank you for chosing our chips.

While you use GR5515I0ND chip, you need to change "EXT_EXFLASH_ENABLE" to "1", this macro definition is also in "custom_config.h".

Have you ever modified it in your code?

903***645

Thanks for the quick response. Yes I tried to set EXT_EXFLASH_ENABLE" to "1 but it did not affect the problem. Below is the contents my of the file "custom_config.h"

#ifndef __CUSTOM_CONFIG_H__

#define __CUSTOM_CONFIG_H__

// <<< Use Configuration Wizard in Context Menu >>>

// <h> Basic configuration

// <o> Chip version

#define GR5515_D

// <o> Select chip type

// <0=> GR5515

// <1=> GR5513

#ifndef CHIP_TYPE

#define CHIP_TYPE 0

#endif

// <o> Enable encrypt chip

// <0=> DISABLE

// <1=> ENABLE

#ifndef ENCRYPT_ENABLE

#define ENCRYPT_ENABLE 0

#endif

// <o> Enable the external flash of chip

// <0=> DISABLE

// <1=> ENABLE

#ifndef EXT_EXFLASH_ENABLE

#define EXT_EXFLASH_ENABLE 1

#endif

// <o> Enable system fault trace module

// <0=> DISABLE

// <1=> ENABLE

#ifndef SYS_FAULT_TRACE_ENABLE

#define SYS_FAULT_TRACE_ENABLE 1

#endif

// <o> Enable APP driver module

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_DRIVER_USE_ENABLE

#define APP_DRIVER_USE_ENABLE 1

#endif

// <o> Eanble APP log module

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_LOG_ENABLE

#define APP_LOG_ENABLE 1

#endif

// <o> APP log port type

// <0=> UART

// <1=> RTT

// <2=> ITM

#ifndef APP_LOG_PORT

#define APP_LOG_PORT 0

#endif

// <o> Eanble APP log store module

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_LOG_STORE_ENABLE

#define APP_LOG_STORE_ENABLE 0

#endif

#if (CHIP_TYPE == 0)

// <o> Enable SK GUI module, only available in GR5515

// <0=> DISABLE

// <1=> ENABLE

#ifndef SK_GUI_ENABLE

#define SK_GUI_ENABLE 0

#endif

#endif

// <o> Enable debug monitor module

// <0=> DISABLE

// <1=> ENABLE

#ifndef DEBUG_MONITOR

#define DEBUG_MONITOR 1

#endif

// <o> Enable DTM test support

// <0=> DISABLE

// <1=> ENABLE

#ifndef DTM_TEST_ENABLE

#define DTM_TEST_ENABLE 0

#endif

// <o> Enable BLE DFU support

// <0=> DISABLE

// <1=> ENABLE

#ifndef DFU_ENABLE

#define DFU_ENABLE 0

#endif

// <o> Protection priority level

// <i> Default: 0

#ifndef FLASH_PROTECT_PRIORITY

#define FLASH_PROTECT_PRIORITY 0

#endif

// <o> NVDS Start Address

// <i> Default: 0x010FF000

#ifndef NVDS_START_ADDR

#if (CHIP_TYPE == 0)

#define NVDS_START_ADDR 0x010FF000

#else

#define NVDS_START_ADDR 0x0107F000

#endif

#endif

// <o> The Number of sectors for NVDS

// <i> Default: 1

#ifndef NVDS_NUM_SECTOR

#define NVDS_NUM_SECTOR 1

#endif

// <o> Call Stack Size

// <i> Default: 0x4000

#ifndef CSTACK_HEAP_SIZE

#define CSTACK_HEAP_SIZE 0x4000

#endif

// <o> Enable callstack backtrace function

// <i> Default: 0

#ifndef ENABLE_BACKTRACE_FEA

#define ENABLE_BACKTRACE_FEA 0

#endif

// </h>

// <h> Boot info configuration

// <o> Code load address

// <i> Default: 0x01002000

#define APP_CODE_LOAD_ADDR 0x01002000

// <o> Code run address

// <i> Default: 0x01002000

#define APP_CODE_RUN_ADDR 0x01002000

// <ol.0..5> System clock

// <0=> 64MHZ

// <1=> 48MHZ

// <2=> 16MHZ-XO

// <3=> 24MHZ

// <4=> 16MHZ

// <5=> 32MHZ-CPLL

#define SYSTEM_CLOCK 0

// <o> External clock accuracy used in the LL to compute timing <1-500>

// <i> Range: 1-500

#define CFG_LF_ACCURACY_PPM 500

// <o> Enable internal osc as low power clock

// <0=> Default: Disable internal osc as low power clock

// <1=> Enable internal osc as low power clock and force CFG_LF_ACCURACY_PPM to 500ppm

#define CFG_LPCLK_INTERNAL_EN 0

// <o> Delay time for Crystal stabilization time

// <i> Default: 100

// <i> Range: 100-500

// <i> Note: Set according to actual measurement data

#ifndef CFG_CRYSTAL_DELAY

#define CFG_CRYSTAL_DELAY 100

#endif

// <o> Delay time for Boot startup

// <0=> Not Delay

// <1=> Delay 1s

#define BOOT_LONG_TIME 1

// <o> In xip mode, check image during cold boot startup

// <0=> Not check

// <1=> Check image

#define BOOT_CHECK_IMAGE 0

// <o> Code version.16bits

#define VERSION 1

// <o> Delay time between flash wakeup and read chip id in warm boot

// <i> Default: 0

// <i> Range: 0-10

// <i> Note:

// <0=> No delay

// <1=> Delay 5 us

// <2=> Delay 10 us

// <3=> Delay 15 us

// <4=> Delay 20 us

// <5=> Delay 25 us

#ifndef EXFLASH_WAKEUP_DELAY

#define EXFLASH_WAKEUP_DELAY 5

#endif

// </h>

// <h> BLE resource configuration

// <i> Note: The total number of BLE Activities(CONNECTIONS+ADVS+2*PER_ADVS+SYNCS+SCAN) should not exceed the limit 12.

// <o> Support maximum number of BLE profiles <0-64>

// <i> Range: 0-64

#ifndef CFG_MAX_PRFS

#define CFG_MAX_PRFS 10

#endif

// <o> Support maximum number of bonded devices <0-10>

// <i> Range: 0-10

#ifndef CFG_MAX_BOND_DEVS

#define CFG_MAX_BOND_DEVS 4

#endif

// <o> Support maximum number of BLE Links <0-10>

// <i> Range: 0-10

#ifndef CFG_MAX_CONNECTIONS

#define CFG_MAX_CONNECTIONS 10

#endif

// <o> Support maximum number of BLE Legacy/Extended Advertisings <0-5>

// <i> Range: 0-5

// <i> Note: The total number of BLE Legacy/Extended/Periodic Advertisings should not exceed the limit 5.

#ifndef CFG_MAX_ADVS

#define CFG_MAX_ADVS 1

#endif

// <o> Support 31 bytes adv data for legacy adv

#ifndef CFG_MAX_ADV_DATA_LEN_SUPPORT

#define CFG_MAX_ADV_DATA_LEN_SUPPORT 0

#endif

// <o> Support maximum number of BLE Periodic Advertisings <0-5>

// <i> Range: 0-5

// <i> Note: The total number of BLE Legacy/Extended/Periodic Advertisings should not exceed the limit 5.

#ifndef CFG_MAX_PER_ADVS

#define CFG_MAX_PER_ADVS 0

#endif

// <o> Support maximum number of BLE Periodic Advertising Synchronizations <0-5>

// <i> Range: 0-5

#ifndef CFG_MAX_SYNCS

#define CFG_MAX_SYNCS 0

#endif

// <o> Support maximum number of BLE Scan <0-1>

// <i> Range: 0-1

#ifndef CFG_MAX_SCAN

#define CFG_MAX_SCAN 1

#endif

// </h>

// <h> MESH support configuration

// <o> MESH support

// <0=> NOT SUPPORT

// <1=> SUPPORT

#ifndef CFG_MESH_SUPPORT

#define CFG_MESH_SUPPORT 0

#endif

// </h>

// <h> LCP support configuration

// <o> LCP support

// <0=> NOT SUPPORT

// <1=> SUPPORT

#ifndef CFG_LCP_SUPPORT

#define CFG_LCP_SUPPORT 0

#endif

// </h>

// <h> APP Driver Basic configuration

// <o> I2C DMA enable

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_DRV_I2C_DMA_ENABLE

#define APP_DRV_I2C_DMA_ENABLE 1

#endif

// <o> I2C INTERRUPT enable

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_DRV_I2C_IT_ENABLE

#define APP_DRV_I2C_IT_ENABLE 1

#endif

// <o> SPI DMA enable

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_DRV_SPI_DMA_ENABLE

#define APP_DRV_SPI_DMA_ENABLE 1

#endif

// <o> SPI INTERRUPT enable

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_DRV_SPI_IT_ENABLE

#define APP_DRV_SPI_IT_ENABLE 1

#endif

// <o> QSPI DMA enable

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_DRV_QSPI_DMA_ENABLE

#define APP_DRV_QSPI_DMA_ENABLE 1

#endif

// <o> QSPI INTERRUPT enable

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_DRV_QSPI_IT_ENABLE

#define APP_DRV_QSPI_IT_ENABLE 1

#endif

// <o> UART DMA enable

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_DRV_UART_DMA_ENABLE

#define APP_DRV_UART_DMA_ENABLE 1

#endif

// <o> UART INTERRUPT enable

// <0=> DISABLE

// <1=> ENABLE

#ifndef APP_DRV_UART_IT_ENABLE

#define APP_DRV_UART_IT_ENABLE 1

#endif

//#define XIP_MODE 1

// </h>

// <<< end of configuration section >>>

#endif //__CUSTOM_CONFIG_H__

Barton

Hi Osipov,

There are two places you can modify, please try it, thanks

1、If chip is encrypted,you need enable the “ENCRYPT_ENABLE”;

2、Since an error occurred in platform_clock_init(), so maybe you can switch to the internal clock by enable the “CFG_LPCLK_INTERNAL_EN”;

903***645

Hi, Barton.

Thanks for your reply, it helped move things along. I solved the problem, the 32768 clock oscillator was missing in the circuit. After installing it the startup code was initialized successfully. But if the clock oscillator is not required for the projected device then how can I do without it?

And please answer the second part of my question about custom_config.h:

#define GR5515_D

#define GR5515_C

#define GR5515_E

What types of chips do they define?

Open WeChat, use "Scan" to follow.