Angelo

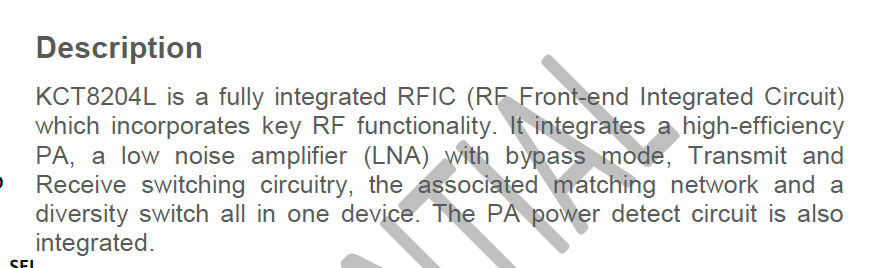

我们现在有一个项目需要外接一个PA,型号如图:

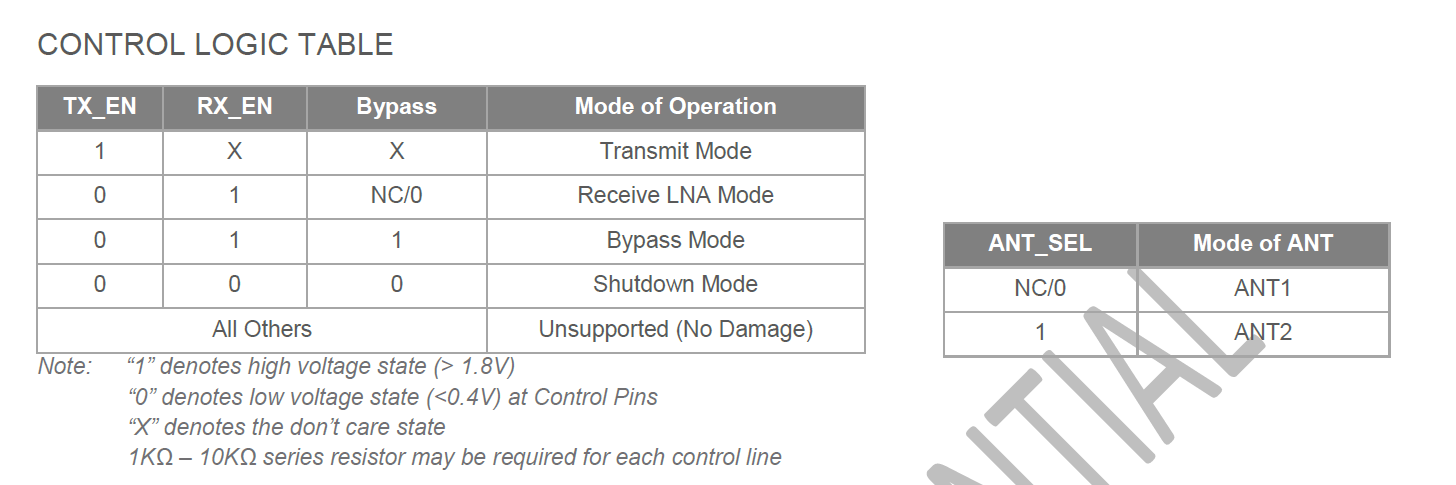

这个PA的控制逻辑如下:

请问你们有没有参考的补丁程序,可以集成类似的PA芯片,或者提供一种思路文档供我们参考呢?多谢!

june

使用该PA的话,需要预留特定GPIO引脚,GPIO2, GPIO3和GPIO6,并且这三个引脚分别和TX_EN, RX_EN和Bypass引脚连接。

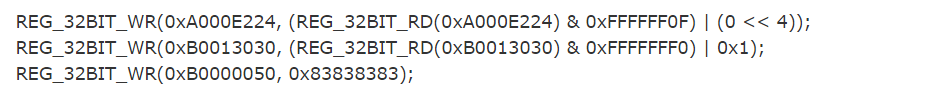

参考代码如下:

#define TX_EN_PIN GPIO_PIN_2

#define RX_EN_PIN GPIO_PIN_3

#define BYPASS_PIN GPIO_PIN_6

#define REG_32BIT_RD(addr) (*(volatile uint32_t *)(addr))

#define REG_32BIT_WR(addr, value) (*(volatile uint32_t *)(addr)) = (value)

void cfg_output_signal_for_pa(void)

{

gpio_init_t gpio_init = GPIO_DEFAULT_CONFIG;

gpio_init.mode = GPIO_MODE_MUX; // Config GPIO_PIN_MUX_TESTBUS for Diagnostic port

// use tx mode & lna mode

gpio_init.pin = TX_EN_PIN | RX_EN_PIN;

// use rx mode & bypass mode

// gpio_init.pin = TX_EN_PIN | RX_EN_PIN | BYPASS_PIN;

gpio_init.mux = GPIO_PIN_MUX_TESTBUS;

hal_gpio_init(GPIO0, &gpio_init);

REG_32BIT_WR(0xA000E224, (REG_32BIT_RD(0xA000E224) & 0xFFFFFF0F) | (0 << 4)); REG_32BIT_WR(0xB0013030, (REG_32BIT_RD(0xB0013030) & 0xFFFFFFF0) | 0x1); REG_32BIT_WR(0xB0000050, 0x83838383);

}

Note:

1. cfg_output_signal_for_pa需要在BLE协议栈初始化结束后调用

2. 如果要关掉FEM,只需要把0xB0000050配为0

3. Bypass模式切换到LNA模式时,需要把GPIO6反初始化

Angelo

十分感谢这个参考代码!很有用,我试试。对了,这段代码有没有相应的文档解释呢?

这几个寄存器配置以后主要实现的是什么作用呢?想学习一下。感觉应该是自动控制 gpio_init.pin = TX_EN_PIN | RX_EN_PIN; 收发自动切换?

june

配置了这些寄存器以后,在RF真正TX和RX之前,会把对应的电平拉高,结束后会把电平拉低。GR551x本身并不用这些信号来控制,但是可以用来控制外接的FEM。

目前这些寄存器没有开放出来,后续可能会出一个外扩PA的参考设计方案。

打开微信,使用“扫一扫”即可关注