2024-07-02

GR5526 GUI专题(4) - Lvgl字体的位图数组合并转换为bin文件的说明

写技术文章

精选推荐

Talon

一、电流路径分析

在进行DCDC PCB layout说明前,先了解一下Buck DCDC在工作时的电流路径,通过电流路径分析来简要阐述DCDC噪声是如何产生的。

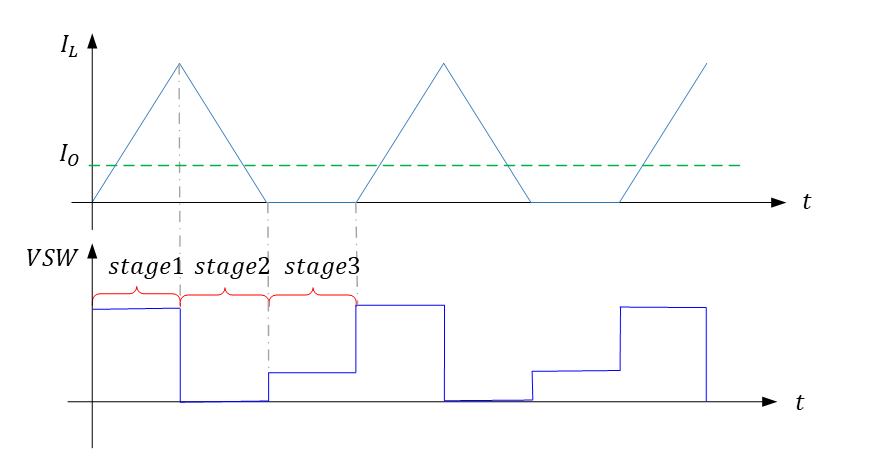

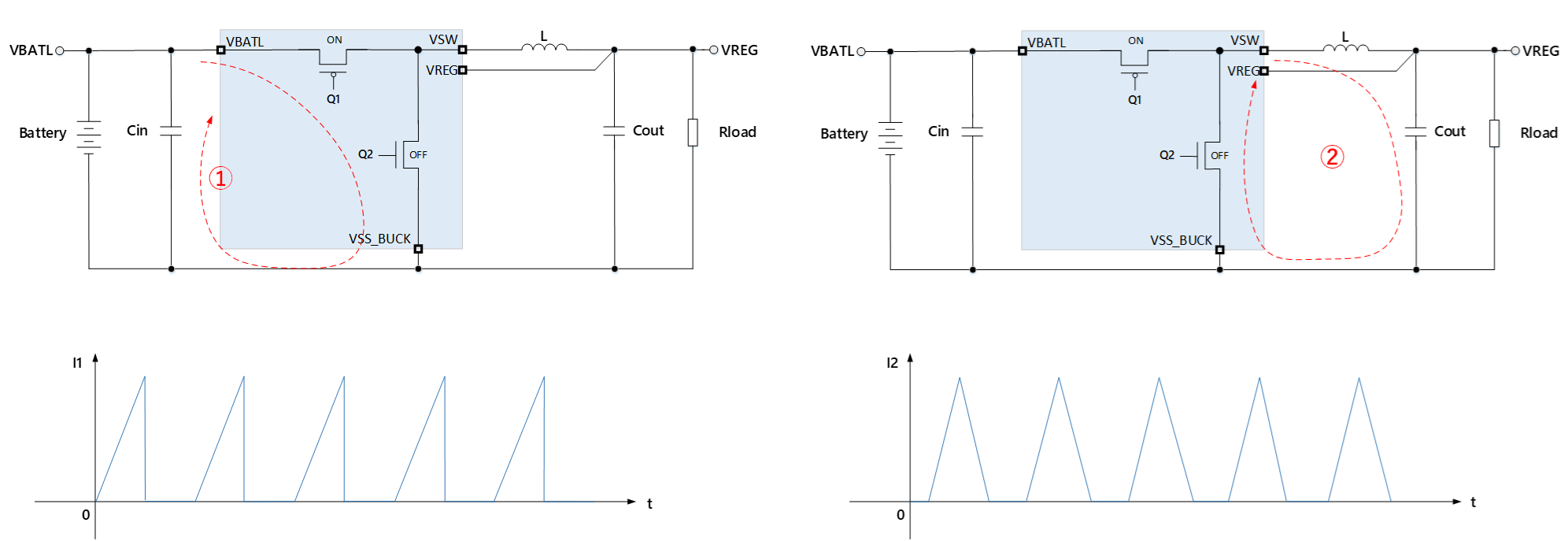

如DCDC系列(一)中基本原理的所述,Goodix BLE SoC的DCDC是一种基于纹波控制的单环COT DCDC架构,且工作在PFM模式,下图5.1便是DCDC工作时3个基本的工作阶段(即stage1、stage2和stage3),我们将基于DCDC不同的工作阶段,来阐述说明各个阶段下的电流路径。

图5.1 COT DCDC基本工作阶段示意图

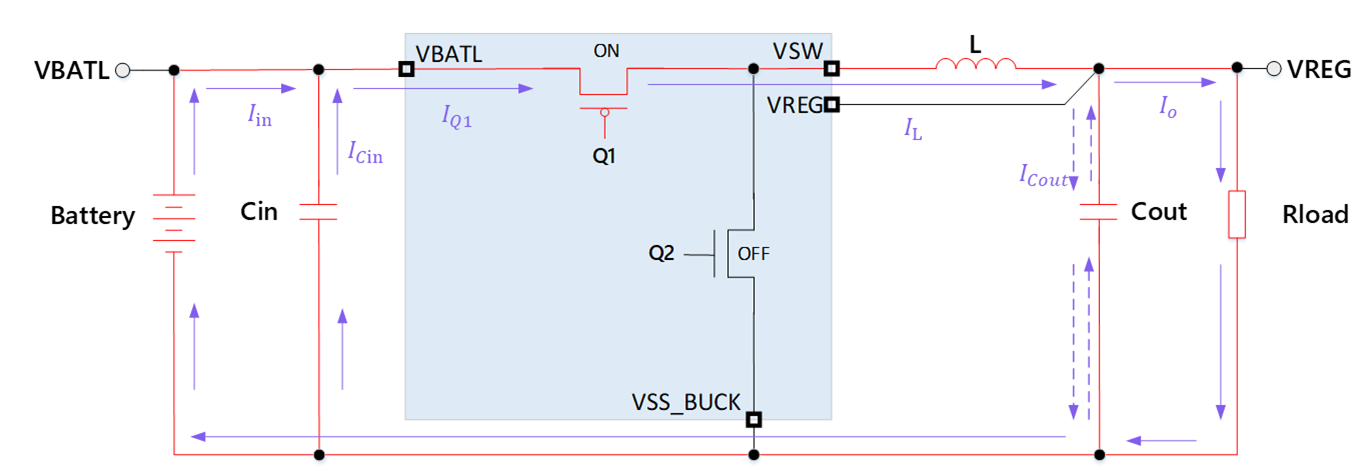

Stage1阶段

Stage1阶段DCDC工作时,DCDC上管Q1导通,下管Q2断开。此时电流Iin路径是从输入电容器Cin到Q1再经过电感L到输出电容器Cout和负载Rload;Icin的电流路径则是经过Q1再经过电感L到输出电容器Cout和负载Rload,即IQ1=Iin+Icin,此阶段输入电容器Cin处于放电状态;输出电容器Cout的状态会先从放电到充电状态,即当IL<Io时,IL不能满足负载电流Io需求,此时输出电容器就会放电,使得Io=IL+Icout,确保负载正常工作,而当IL>Io时,IL在满足负载电流Io需求后,会同时再给输出电容器Cout充电。整个电流路径如图5.2所示。

图5.2 stage1电流路径示意图

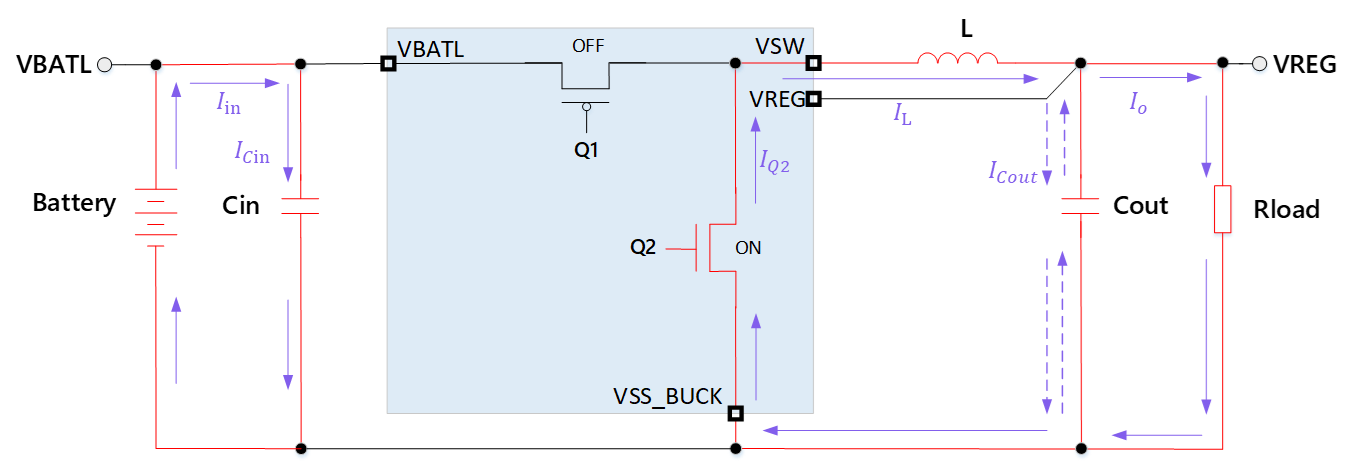

Stage2阶段

Stage2阶段DCDC工作时,DCDC上管Q1断开,下管Q2导通。此时输入电流 路径是直接给输入电容器Cin充电;而且此阶段电感 在其反向电动势的作用下维持输出电流Io,刚开始阶段IL>Io,因此IL在满足负载电流Io需求后,会同时再给输出电容器Cout充电,而随着电感能量减弱,当IL<Io时,IL不能满足负载电流Io需求,此时输出电容器就会放电维持输出电流Io,使得Io=IL+Icout,确保负载正常工作。整个电流路径是电感 经过负载Rload到Q2,如图5.3所示。

图5.3 stage2电流路径示意图

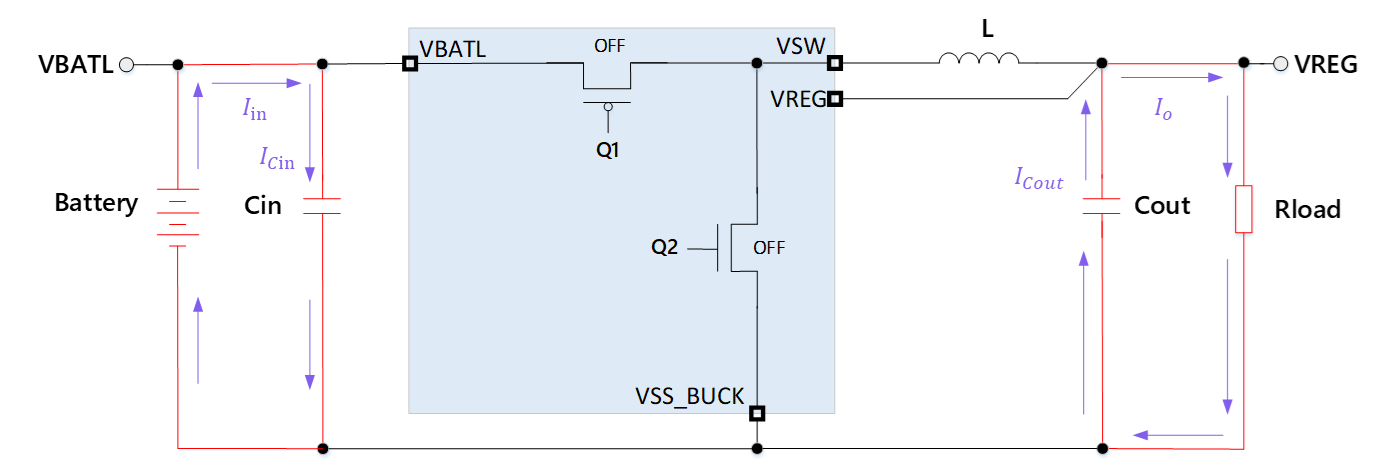

Stage3阶段

Stage3阶段DCDC工作时,DCDC上管Q1和下管Q2均断开。此时输入电流Iin依然是只给输入电容器Cin充电;输出电容器Cout工作在放电状态,作为唯一的电源给负载提供所需的输出电流Io,确保负载正常工作。整个电流路径如图5.4所示。

图5.4 stage3电流路径示意图

二、两个重要的环路

如上述电流路径介绍,可以清晰地看出,其DCDC输入环路和输出环路的电流均是断续的,且环路①和环路②的电流如图5.5所示,环路电流波动幅度都很大,电磁辐射均强,其中环路①的电流会从峰值IL_peak突变到0,其所携带的噪声谐波分量较环路②更高;因此在layout布局时,环路①和环路②都要做到最小。

图5.5

三、敏感信号远离高频干扰源

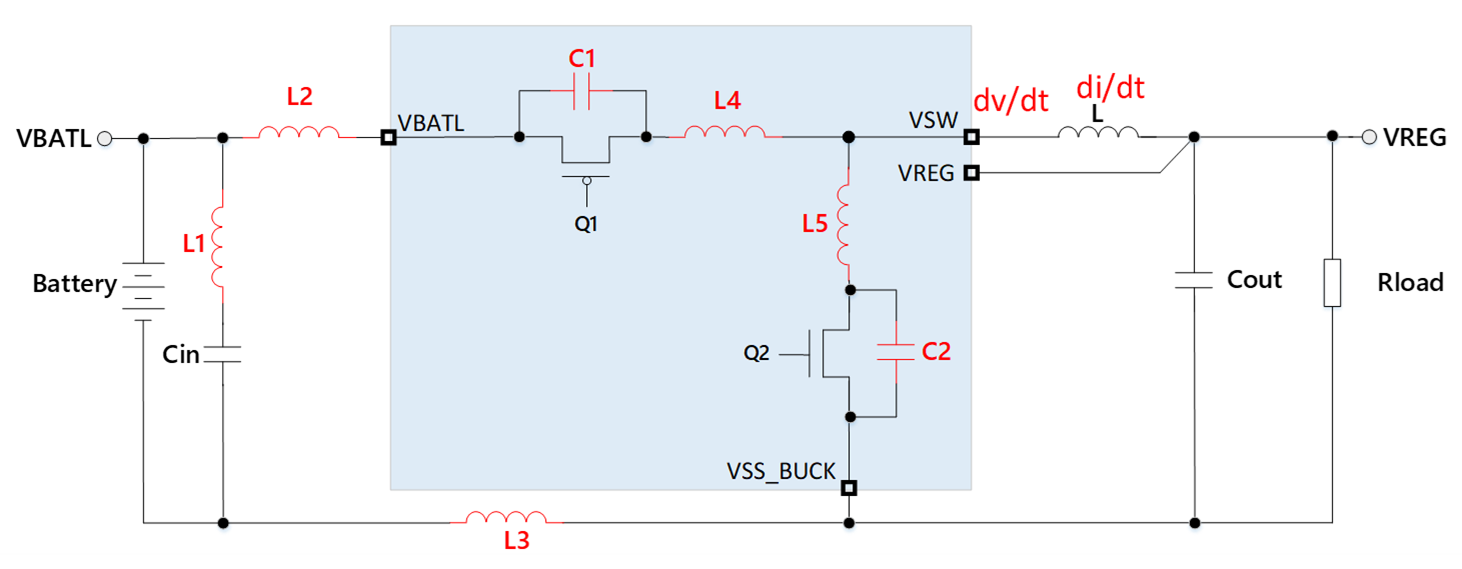

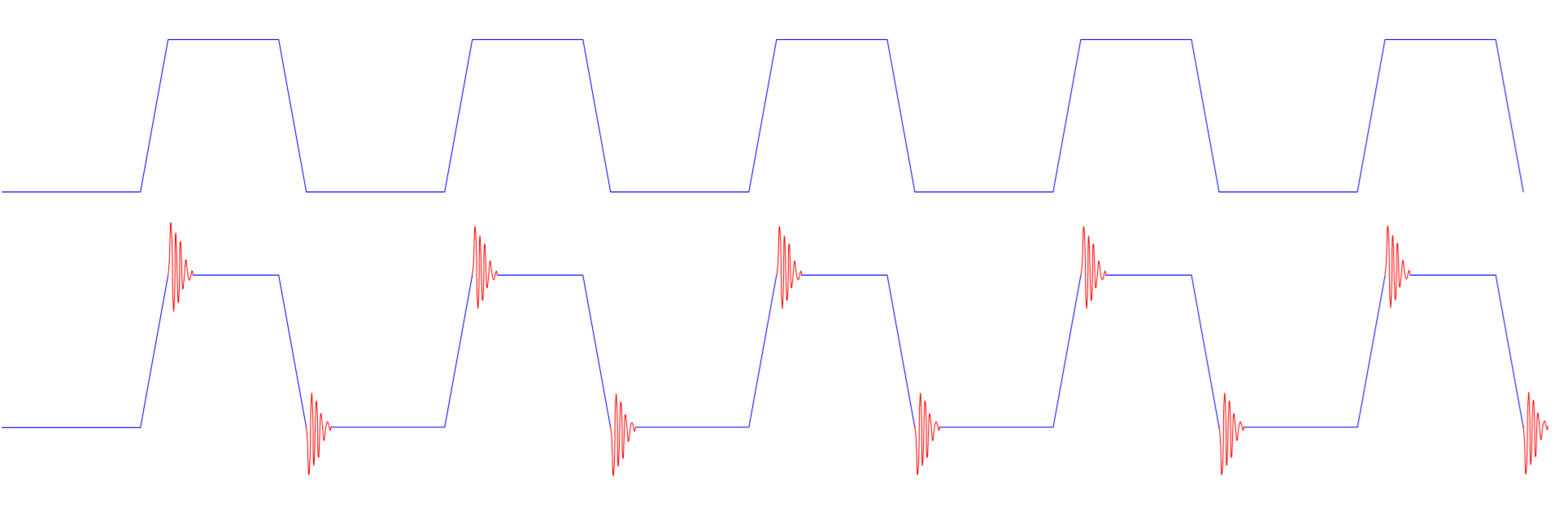

两个重要的环路主要是从电流不连续的角度来阐明输入输出环路面积要尽可能减小,降低高频EMI辐射干扰,影响RF等信号。本小节则着重于DCDC模块各器件寄生电容参数(C1/C2)和走线分布寄生电感(L1/L2/L3/L4/L5)的影响,其寄生参数基本模型如图5.6所示;由于寄生参数的影响,使得上下管开关时产生的VSW信号边沿并不是理想的信号,信号边沿会产生高频振铃,如图5.7所示。所产生的电流和电压干扰信号可以通过以下两个基本公式计算:

(33)

(34)

图5.6

图5.7

在进行PCB layout设计时,需要将XO/RTC时钟信号、RF走线和VREG等对噪声敏感的信号,远离这类噪声干扰源,并对DCDC高频噪声(例如VSW)节点做好接地隔离防护,如果此类高频干扰源隔离做的不够好,就会明显的出现RF sensitivity差等问题。

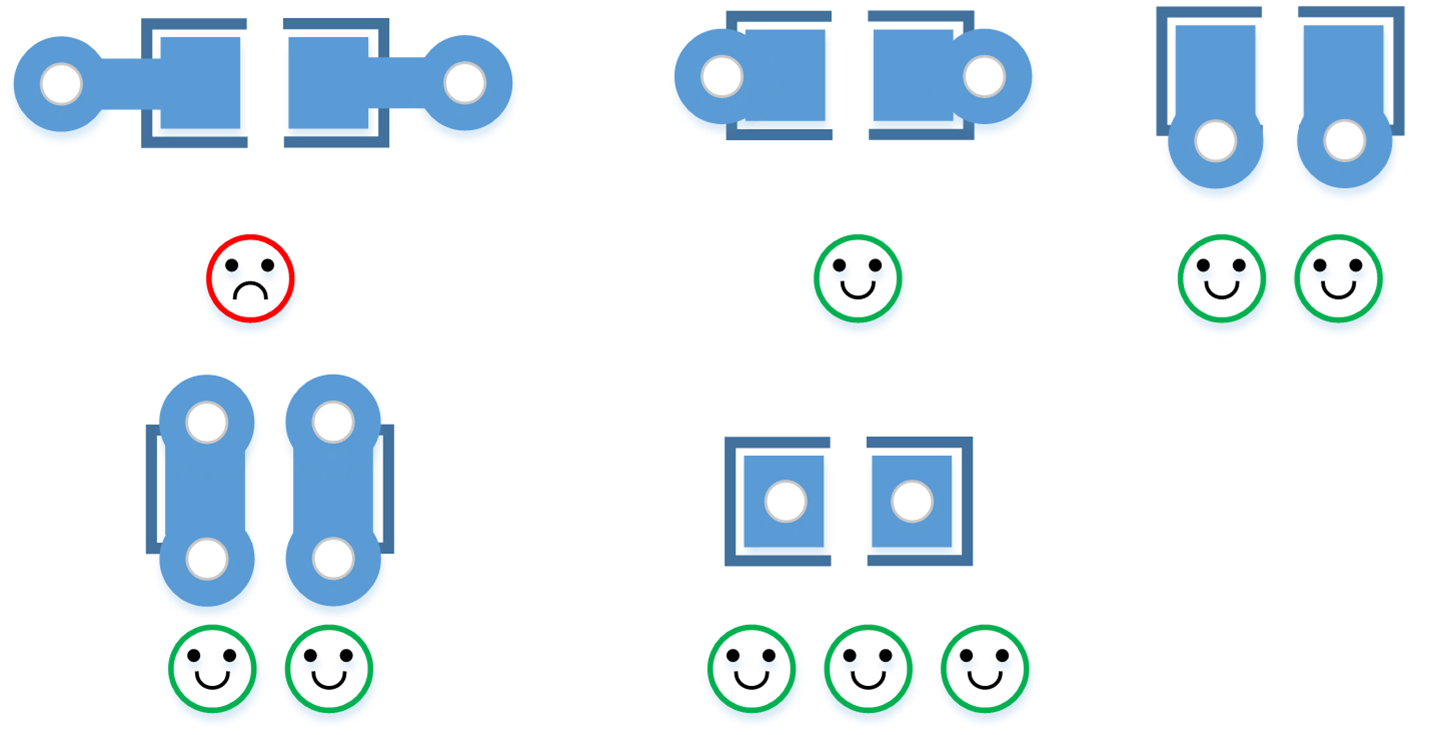

四、如何设计过孔降低寄生参数

摆放过孔的基本原则就是环路面积最小,从而使得寄生电感参数最小。如下图5.8是集中过孔放置方式的对比,其中第一种是最差的,会引入较大的寄生电感;第二种方式相较于第一种过孔方式,缩短了焊盘与过孔之间的走线距离,其环路面积减小,寄生电感也变小。第三种方式采用侧边打孔方式,相比于第二种方式,进一步减小环路面积,是比较好的一种方式;第四种方式则是采用两侧打孔的方式,相比于第三种方式,增加了侧边过孔并联数量,使得寄生电感参数相比于第三种打孔方式更小;第五种打孔方式是最佳的打孔方式,即将过孔打在焊盘中心,这样环路面积最小,寄生电感参数也最小,但是使用此种打孔方法需要注意焊接问题,在SMT时,盘上孔很容易导致焊锡流失,导致虚焊。

图5.8

针对体积较大的元器件,可以将过孔打在器件内侧,根据器件焊盘间隔距离,可以错位打孔或并排打孔,如下图5.9所示。

图5.9

五、参考设计分享

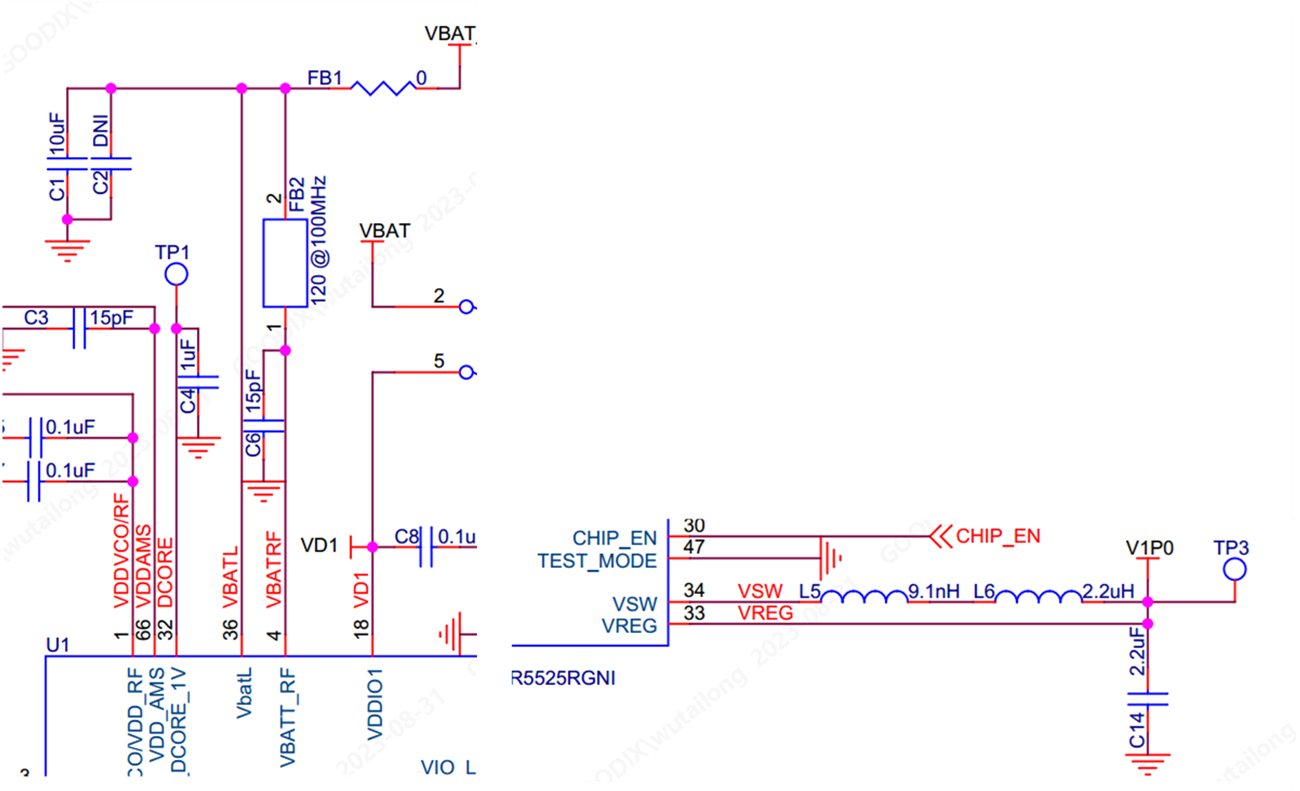

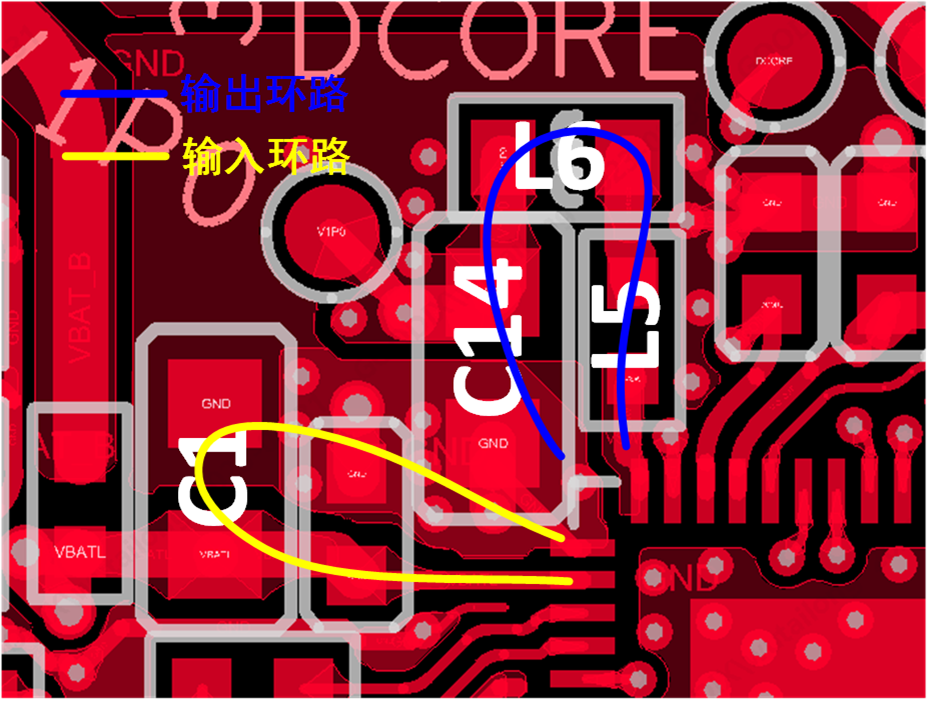

基于GR552x系列芯片,如下给出一个PCB layout示例,详细请查看相关芯片的硬件设计指南。

图5.10 GR552x DCDC部分原理图

图5.11 GR552x DCDC PCB layout示例

打开微信,使用“扫一扫”即可关注