2024-07-02

GR5526 GUI专题(4) - Lvgl字体的位图数组合并转换为bin文件的说明

写技术文章

精选推荐

Talon

一、前言

Buck DCDC的基本框架主要分为传统电压环DCDC、传统电流环DCDC、和COT(Constant ON-Time) DCDC等几类,其基本框架如下介绍。

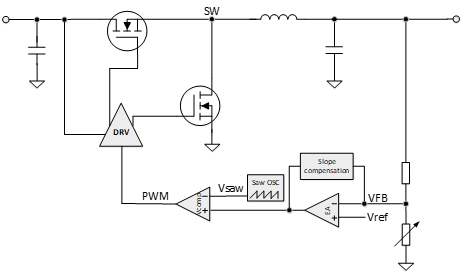

传统电压环DCDC

电压环DCDC属于单环控制模式,有且仅有输出电压反馈环,内部Saw OSC振荡器产生的信号波形幅度大,抗噪能力强;但它的瞬态响应很慢,原因是为了优化次谐波振荡,需要在误差放大器位置对VFB进行斜坡补偿,使得DCDC系统稳定;且无电流限功能。

图1.1 传统电压环DCDC架构

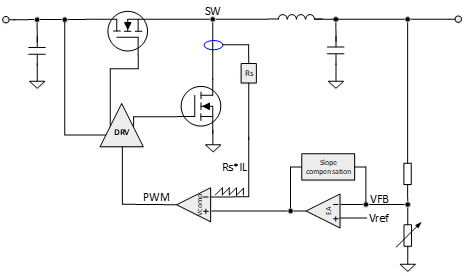

传统电流环DCDC

电流环DCDC属于双环控制模式,根据电流检测的位置,分为峰值电流环控制模式、谷值电流环控制模式和平均电流环控制模式,主要由输出电压反馈环和电流环两个环路来实现控制,其瞬态响应比电压环更好,且有自动限流的功能,但仍需要斜坡补偿网络,且对噪声敏感。

图1.2 传统电流环DCDC架构(谷值电流)

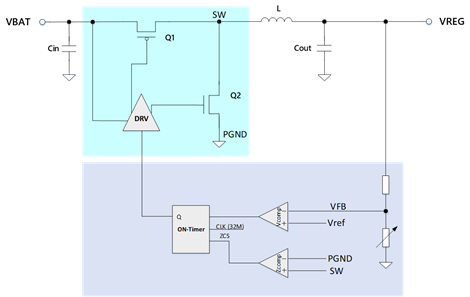

单环COT DCDC

单环COT DCDC,区别于传统电流环和电压环DCDC,它的主要特点是没有复杂的斜坡补偿电路,只是将输出电压VFB的纹波谷值与比较器的Vref比较,输出触发生成固定导通时间脉冲来驱动DCDC上管导通;其瞬态响应极快。

图1.3 单环 COT DCDC架构

二、BLE SoC PFM COT DCDC基本框架

Goodix的GR551x、GR552x和GR533x系列BLE SoC,其片上DCDC模块采用了COT DCDC框架模式,是一种基于纹波控制的单环COT DCDC架构,其中ZCS(Zero-current switch,零电流开关)是通过检测谷电流来实现下管Q2的关断,基本框图如图1.4所示:

图1.4 COT DCDC框架图

三、基本工作原理

图1.5 工作时序波形图

l Stage1:VFB纹波谷电压低于Vref电压时,触发状态机,在CLK上升沿位置打开PMOS(Q1),上管PMOS导通时间=TON值*Tosc,此时电感电流IL上升,此阶段测的VSW pin位置的电压为VBAT电压;

l Stage2: 当上管PMOS导通TON值*Tosc后,状态机即刻关闭上管PMOS,打开下管NMOS(Q2),电感电流开始下降,此阶段测的VSW pin位置的电压为0V电压,当电感电流下降至0mA附近时,电感电流开始反向,此时PGND电压大于VSW处电压,状态机触发关闭下管NMOS;

l Stage3: 在下管NMOS打开阶段,由于后级负载此时间段内消耗的电量较少,所以VFB还未低至Vref,所以此阶段中,上管PMOS和下管NMOS均处于关断状态,此时的电感电流为0mA,此阶段测的VSW上的电压就是Cout上的电压VREG;

l Stage4: 随着负载的持续消耗,Cout电压降低,导致VFB电压低于Vref,此时触发状态机,在CLK上升沿位置打开PMOS,再次重复stage1/2/3过程。

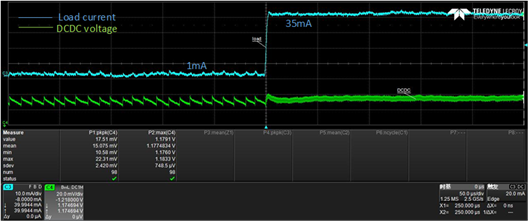

四、架构的优点

1) 有极好的瞬态负载响应,更适用于CPU/GPU core供电,实测load transient波形如下所示

图1.6 COT DCDC框架示意图

2) DCDC效率基本与负载大小无关;

3) 控制环路设计复杂度低,DCDC内部不需要做斜坡补偿,易于实现;

五、架构的缺点

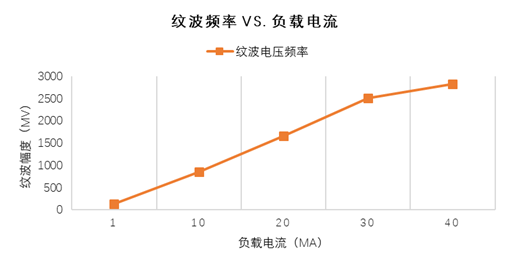

1) 纹波不恒频,纹波频率随着负载变化而变化,对噪声敏感;

图1.7 纹波频率与负载电流的关系曲线

2) COT DCDC的稳定性建立在纹波上的,若VFB上的纹波很小或与电感电流存在较大相位差,且控制环内没有纹波补偿,会引入稳定性问题,因此需要选择合理的输出电容值,详细原因将在DCDC系列(二)中说明。

打开微信,使用“扫一扫”即可关注